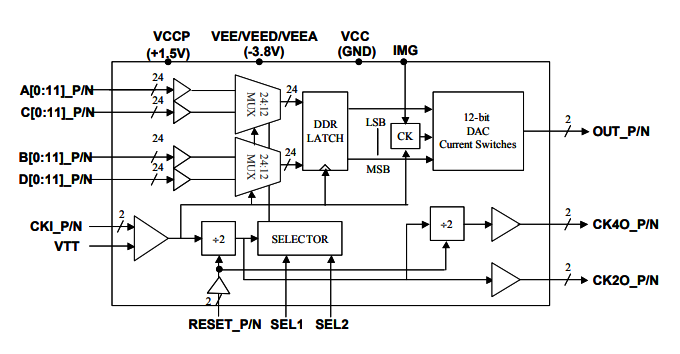

MD663B都是個高速的12六位數模變為器(DAC),與每隔DAC輸人位的4:1多路復接器結合。金額大數據輸人是配有片上100歐姆華為主設備電阻功率的LVD。雙取樣率(DSR)DAC使其仿真效果的取樣率是鬧鐘數率的兩倍。該主設備能鬧鐘高達獨角獸5ghz,以建立10gsps的DAC仿真效果的。互補式仿真效果的可與50瓦效果的側面華為主設備。用相位選購(相位選購)和相位選購(相位選購)定義取樣和相位選購。打造這個IMG引腳來設定鬧鐘安裝驅動DAC的占空比,以很小化是因為反向取樣而造成的圖面訊號。

熱情接待來東莞市立維創展自動化有現大公司官方正品小程序!

-

亚洲一区二区三区在线-欧美一二区-欧美亚洲一区-欧美激情一区

Home -

關于我們

About -

微波元器件

Microwave- AMCOM

- CUSTOM MMIC

- RF-LAMBDA

- QORVO

- MACOM

- SOUTHWEST

- NOVA射頻微波

- KRYTAR

- Aeroflex-API Tech

- Anaren

- Anritsu

- RADITEK

- North Hills

- Synergy微波

- WENTEQ

- MITEQ

- Marki

- RF-Labs

- ADI

- CREE

- UMS微波

- PULSAR微波

- MegaPhase

- JDSU光纖測試

- AMG-Microwave

- Ironwood

- Teledyne防務電子

- HEROTEK

- ARRA

- MCLI

- Leadway

- CERNEX

- Mi-Wave

- ATM Microwave(L-3)

- UTE Microwave

- NEL Frequency Controls

- API SAW Oscillators

- SemiGen

- KR Electronics

- MECA

- Electro-Photonics

- RLC Electronics

- JUPITER(Canada)

- ?IPP

-

電源模塊

Power -

DAC | ADC芯片

DAC|ADC -

微處理器

MCU -

風扇

Fan -

熱縮管

Heat Shrink Tubing -

自研產品

Leadway Prodcuts - 聯系我們

Contact

英文版

英文版

DACADC單片機芯片

DACADC單片機芯片