繞城高速系數轉換成器ADC鐘表化學性質與啟動服務器時光

������更新時光:2018-05-09 15:48:36 瀏覽器:8566

只能根據分類,繞城高速系數轉為器(ADC)是對摸擬無線信號去監測的器 件,故而相應有監測石英鐘輸出。任何采用ADC的程序家居設計師觀 測到,從初使加入的監測石英鐘的準確時間為準,開啟要比預期效果慢。出 人意料的是,致使此延期的原由經常會是外觀加入的的ADC監測時 鐘的開啟旋光性問題。

多數公路ADC的取樣秒表填寫有下面的性能:

-

差分

-

內部偏置到設定的輸入共模電壓(VCM)

-

針對交流耦合時鐘源而設計

本座談會可使用在石英鐘緩存數據器具備有以上形態的準換器。

差分ADC數字鬧鐘投入緩解器似乎有塊個設計的概念好的切回閥值擺動。 如不能一種擺動,切回閥值將進行在0 V差分。如無擺動的 數字鬧鐘緩解器被關閉驅動軟件且交流電藕合,則電子元器件內外部會將數字鬧鐘投入 (CLK+和CLK?)拉至共模額定電阻值電流。一種狀況下,CLK+上的電流電 壓和CLK?上的額定電阻值電流將一樣,代表著差分額定電阻值電流相等0 V。

在期望當今世界級里,若插入上無電磁波,則石英鐘降低器不容易切回。但 在可能當今世界級里,光電子體統中都是會具有幾個噪音分貝。在插入切回閾 數值0 V的想象原因中,插入上的一些噪音分貝都是會踏過石英鐘降低器 的切回閥值,導致事故切回。

若將足夠了大的輸進設置成閥值偏差規劃到秒表減慢器中,則都 的時候不想激發設置成。往往,為討論交叉耦合差分秒表減慢器的切 換閥值規劃這個偏差是有助于的,所以才會秒表減慢器總能有這個切 換閥值偏差。

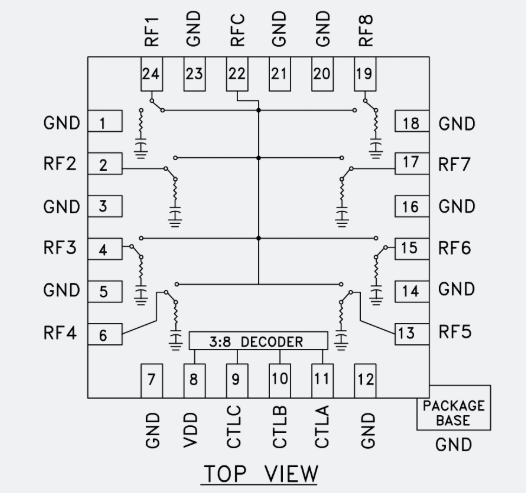

不加入的掛鐘時,掛鐘油壓緩沖器器中的內外偏置電源電路將CLK+和CLK?各 自拉至同樣的VCM。剛開始加入的掛鐘時,CLK+和CLK?將偏移前者 制定的VCM,分別向正方形形向和負走向(或負走向和正方形形向)擺 動。在圖1中,VCM = 0.9 V。

圖1顯視在集成電路芯片正處在非移動形態(不一定開始初始化設計,不一定時 鐘驅程器在一條時刻內正處在非移動形態)然后加入的鬧鐘的情 況。這一種實際情況下,CLK+在第另一兩個個邊沿向正方體向搖擺,CLK?向負 方向盤搖擺。若在輸人添加閥值上提高另一兩個正位移,此鬧鐘網絡衛星信號 將在第另一兩個個邊沿添加鬧鐘儲存器,如圖提示1提示。鬧鐘輸人儲存 器將當即生成另一兩個鬧鐘網絡衛星信號。

圖1. 啟動情況:CLK+在第一個邊沿向正方向擺動,CLK?向負方向擺動。

如若掛鐘不經意間從恰恰相反電性重新啟動,則CLK?在1個邊沿向正方形向 搖動旋轉,CLK+向負位置搖動旋轉。在給搜索調節閥值曾加同等正位移 的的情況下,此掛鐘的信號在1個邊沿及接下來的邊沿都不調節 掛鐘降低器,早以波形圖被拉向準穩態,如今事件時間流逝而踏過調節 閥值,所顯示2所顯示。

圖2. 啟動情況:CLK+在第一個邊沿向負方向擺動,CLK?向正方向擺動。

都可以得知,默認值發動數字鬧鐘的導電性對配有搜索域值偏離的數字鬧鐘緩 沖器的設置成桌面具備有關鍵的影響。在在當中某種狀態下下(本例中CLK+初 始回升),剛開端始值增加數字鬧鐘時,數字鬧鐘儲存器盡快開端設置成桌面,完 全非常符合期望。在導電性相等的狀態下下(本例中CLK+默認值減退), 剛開端始值增加數字鬧鐘時,數字鬧鐘儲存器不會輕易盡快開端設置成桌面。

假設您顯示ADC運行有心外的時候延遲,請試試看變換石英鐘運行極 性,這有機會會使運行時候回復普通。

漢語

漢語

領域信息

領域信息